நினைவகங்கள்...

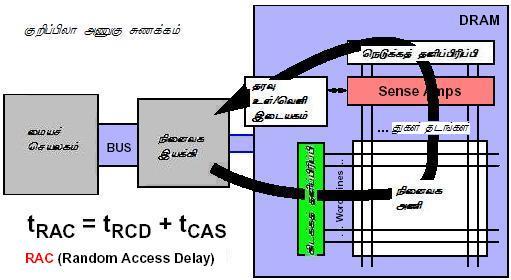

DRAMஇன் கட்டமைப்பு கீழே வரைந்துள்ளது:

DRAM நினைவகங்களில் ஒரு முக்கியமானத் தேவை புதுப்பித்தல்

(Refreshing). முன்பு கூறப்பட்டது ஒரு DRAM கலத்தில் தரவு மின் தேக்கி மூலமாக

சேகரிக்கப்படுகிறது. DRAM நினைவத்தின் அணுகலில் ஒரு குறிப்பிட்ட வரிசைமுறையில் செயல்படுத்தப்படுகிறது. திறன் நிகழ்ந்தவுடன் ஒரு குறன்ந்த பட்ச காலத்திற்கு-பல 100ms வரை எழுதவோ படிக்கவோ இயலாது. ஒரு DRAM தரவுத்தாளில் ஸகஜமாக காணப்படும் எண்விவரங்களில் வருமாறு குறிப்பிட்டுளன:

குறைந்தபட்ச புதுப்பித்தல் வீதம் - Minimum Refresh Rate - Fref - நினைவக கல மின்தேக்கி தரவு முழுதாக வடியப்படும் நேரம்

கிடக்கம் செயல்படுத்தும் சுணக்கம் - Row Activation Delay - Tact - கிடக்கம் முதல்முறை அணுகலில் திறக்கப்படும் நேரம்

கிடக்க அணுகல் சுணக்கம் - Row Access Delay - என்பது ஒரு கிடக்கம் செயல்படுத்தப்பட (ACTIVATION) தொடக்கத்திலிருந்து செயல்விலகபடுவரையான (DEACTIVATION) நேரம். கிடக்கத்தின் செயல்படுத்துதல் செயல்படுத்து ஆணை (ACTIVATE COMMAND) மூலமாகவும் செயல்விலகல் முன்மின்னூட்டு ஆணை (PRECHARGE COMMAND) மூலமாக நிகழ்கிறது.

நெடுக்க அணுகல் சுணக்கம் - Column Access Delay - Tcas - உணர் மிகைப்பியிலிருந்து நினைவக இயக்கிவரை சுணக்கம்

கிடக்க ஆணைச் சுணக்கம் - Row Command Delay - Trcd - நினைவக அணியிலிருந்து உணர் மிகைப்பிவரையான சுணக்கம்

குறிப்பிலா அணுகல் சுணக்கம் - Random Access Delay - DRAM நினைவகக்

கலத்திலிருந்து நினைவக இயக்கிவரை சுணக்கம் - Trac = Trcd + Tcas

கிடக்க முன்மின்னூட்டல் சுணக்கம் - Row Precharge Delay Trp - ஒரு கிடக்கத்தின் அணுகல் முடித்து அடுத்த கிடக்க அணுகல் தொடங்கும் குறைந்தபட்ச இடைவேளை

கிடக்கங்கள் படிப்பு வீதம் - Row reading speed - Trc = Trac + Trp

<<<முந்தியப் பக்கம் /

அடுத்தப் பக்கம்>>>

(c) பதிப்புரிமை தொழில்நுட்பம்/THOZHILNUTPAM.COM

புதுப்பிப்பு ஞாயிறு, 4 ஏப்ரில், 2004